# FIELD–PROGRAMMABLE ANALOG ARRAYS: A FLOATING–GATE APPROACH

A Dissertation Presented to The Academic Faculty

by

Tyson S. Hall

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

School of Electrical and Computer Engineering Georgia Institute of Technology July 12, 2004

Copyright  $\bigodot$  2004 by Tyson S. Hall

# FIELD–PROGRAMMABLE ANALOG ARRAYS: A FLOATING–GATE APPROACH

Approved by:

Professor David V. Anderson, Advisor

Professor Aaron Lanterman

Professor David Citrin

Professor Paul Hasler

Professor Milos Prvulovic

Professor Sudhakar Yalamanchili

Date Approved: July 9, 2004

### ACKNOWLEDGEMENT

Research is rarely pursued in a vacuum. I am grateful to each and every friend for their support, encouragement, assistance, and influence. My advisor, Dr. David Anderson, has been with me every step of the way. I am most thankful for his thoughtful guidance, understanding, and friendship. My co–advisor, Dr. Paul Hasler, has been a continual source of knowledge and encouragement. If it were not for Paul, I would still be ignorant of floating–gate transistors and even FPAAs.

I count it a privilege to know each one of the many graduate students in the Cooperative Analog/Digital Signal Processing (CADSP) group. In particular, I recognize David Graham and Paul Smith for their assistance during my early days of VLSI layout. I am also grateful for the talent and skills that Chris Twigg, Jordan Gray, and Dave Abramson have brought to the FPAA research team. We have spent many long hours together working on layout, testing FPAA chips, and discussing all things FPAA. I also appreciate the time and effort that Sourabh Ravindran has spent working on analog implementations of his feature extraction algorithms. Sourabh is one of my longest and best friends in the CADSP group.

If I did not have such a great team of editors, reading this document would have been much more tedious. In particular, Julie Hall (cousin), Vicki Hall (mother), Burton Hall (father), Barry Hall (brother), and Dr. Roger Hall (uncle) all graciously read rough drafts of this thesis and/or gave editorial assistance despite their varying levels of interest in the topic.

I thank my friends and family who have kept me in their thoughts and prayers during my tenure at Georgia Tech. To the Creator of all that is and was and is to come, I am most grateful. As my knowledge increases, my awe of His handiwork abounds.

## TABLE OF CONTENTS

| ACKNO  | OWLEDGEMENT                                  | iii |

|--------|----------------------------------------------|-----|

| LIST O | F TABLES                                     | vi  |

| LIST O | F FIGURES                                    | vii |

| SUMM   | ARY                                          | ix  |

| CHAPT  | TER 1 RAPID PROTOTYPING OF ANALOG SYSTEMS .  | 1   |

| 1.1    | Low–Power Signal Processing                  | 2   |

| 1.2    | Cooperative Analog/Digital Signal Processing | 4   |

| CHAPT  | TER 2 HISTORY AND MOTIVATION                 | 8   |

| 2.1    | Background on FPAAs                          | 8   |

| 2.2    | Discrete-time FPAAs                          | 9   |

| 2.3    |                                              | 11  |

|        |                                              | 12  |

|        |                                              | 15  |

| 2.4    |                                              | 17  |

| 2.5    | Performance                                  | 19  |

| 2.6    | Application Focus                            | 20  |

| CHAPT  | TER 3 BUILDING A LARGE–SCALE FPAA            | 21  |

| 3.1    |                                              | 21  |

| 3.2    |                                              | 24  |

| 3.3    |                                              | 27  |

| 3.4    |                                              | 31  |

|        |                                              | 33  |

|        |                                              | 34  |

|        |                                              | 35  |

| 3.5    |                                              | 37  |

| CHAPT  | <b>FER 4 RASP 1.0</b>                        | 40  |

| 4.1    |                                              | 41  |

| 4.2    | - 0                                          | 42  |

|        | 0 1                                          | 43  |

|        | 0                                            | 44  |

|        |                                              | 46  |

| 4.3    |                                              | 47  |

|        | 4.3.1 Floating-gate Switches                 | 48  |

| 4.4    |                                              | 50  |

| 4.5    | System Results                               | 52  |

| 4.6         | Summary                                                                                                                             | 5  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

| CHAP        | TER 5 RASP 1.5                                                                                                                      | 59 |  |  |  |  |

| 5.1         |                                                                                                                                     | 59 |  |  |  |  |

|             |                                                                                                                                     | 59 |  |  |  |  |

|             |                                                                                                                                     | 52 |  |  |  |  |

| 5.2         |                                                                                                                                     | ;3 |  |  |  |  |

| 5.3         | Testbed FPAA                                                                                                                        |    |  |  |  |  |

| 5.4         | System Results                                                                                                                      |    |  |  |  |  |

| -           |                                                                                                                                     | 58 |  |  |  |  |

|             |                                                                                                                                     | 2  |  |  |  |  |

|             |                                                                                                                                     | '3 |  |  |  |  |

|             | -                                                                                                                                   |    |  |  |  |  |

|             |                                                                                                                                     | 80 |  |  |  |  |

| 6.1         |                                                                                                                                     | 80 |  |  |  |  |

|             | 1                                                                                                                                   | 31 |  |  |  |  |

|             | 0                                                                                                                                   | 82 |  |  |  |  |

| 6.2         | 8 8                                                                                                                                 | 33 |  |  |  |  |

|             | 1 1                                                                                                                                 | 33 |  |  |  |  |

|             | 0                                                                                                                                   | 87 |  |  |  |  |

|             | 6.2.3 Low-level C Code                                                                                                              | 87 |  |  |  |  |

| CHAP        | TER 7 FPAAS: A ROADMAP TO THE FUTURE                                                                                                | 39 |  |  |  |  |

| 7.1         | Next–generation RASP                                                                                                                | 39 |  |  |  |  |

|             | о́                                                                                                                                  | 0  |  |  |  |  |

|             |                                                                                                                                     | )1 |  |  |  |  |

| 7.2         | · 0                                                                                                                                 | )5 |  |  |  |  |

| 7.3         | Testbed Applications for Large–Scale FPAAs                                                                                          |    |  |  |  |  |

|             |                                                                                                                                     | )7 |  |  |  |  |

|             | 7.3.2 Neuromorphic Modeling                                                                                                         | 0  |  |  |  |  |

| 7.4         | Future Research                                                                                                                     | 2  |  |  |  |  |

|             | 7.4.1 Enabling Technologies                                                                                                         | 3  |  |  |  |  |

|             | 7.4.2 Computational Elements                                                                                                        | 3  |  |  |  |  |

|             | 7.4.3 CAD Tool Flow for Analog Systems                                                                                              | 4  |  |  |  |  |

| 7.5         | Commercialization                                                                                                                   | )5 |  |  |  |  |

| 7.6         | Original Contributions                                                                                                              |    |  |  |  |  |

| 7.7         | Conclusion                                                                                                                          |    |  |  |  |  |

| DFFF        | <b>RENCES</b>                                                                                                                       | 10 |  |  |  |  |

| <b>NELE</b> | $\mathbf{RENCES} \dots \dots$ | 0  |  |  |  |  |

## LIST OF TABLES

| Table 1 | Summary of Signal Processing Functionality | 5  |

|---------|--------------------------------------------|----|

| Table 2 | Summary of FPAA Granularity                | 10 |

### LIST OF FIGURES

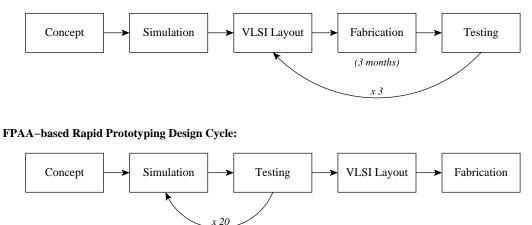

| Figure 1  | Analog design cycle: Traditional vs. FPAA–enabled                                                    | 2    |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------|------|--|--|--|

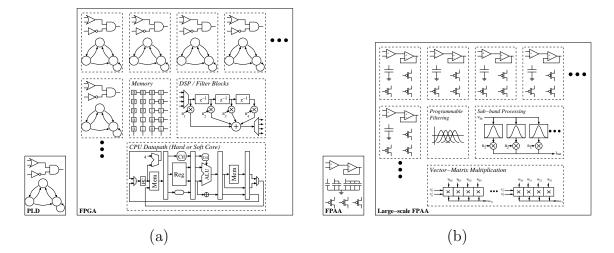

| Figure 2  | FPAA to FPGA analogy                                                                                 |      |  |  |  |

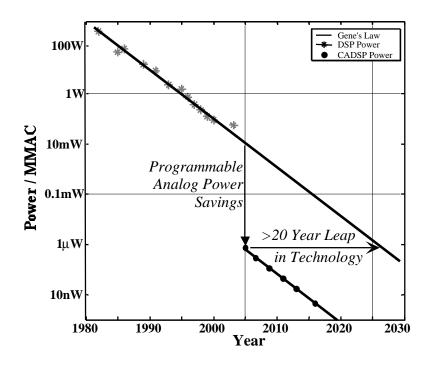

| Figure 3  | Gene's law                                                                                           |      |  |  |  |

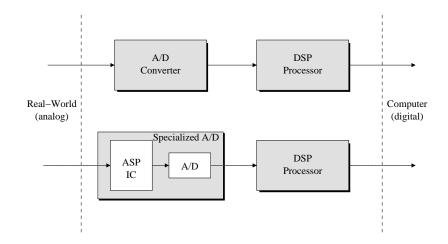

| Figure 4  | Moving the analog/digital boundary                                                                   |      |  |  |  |

| Figure 5  | Switched–capacitor designs                                                                           |      |  |  |  |

| Figure 6  | Summary of interconnect designs                                                                      |      |  |  |  |

| Figure 7  | Current mirror circuit diagrams: with and without switches 2                                         |      |  |  |  |

| Figure 8  | Inverter circuit diagrams: with and without switches                                                 |      |  |  |  |

| Figure 9  | Effects of switches in an FPAA–implemented digital inverter 24                                       |      |  |  |  |

| Figure 10 | Switch network designs: Full crossbar                                                                |      |  |  |  |

| Figure 11 | Switch network designs: Full binary–tree                                                             | 26   |  |  |  |

| Figure 12 | Operational transconductance amplifier circuit diagram: with and                                     |      |  |  |  |

|           | without switches                                                                                     | 28   |  |  |  |

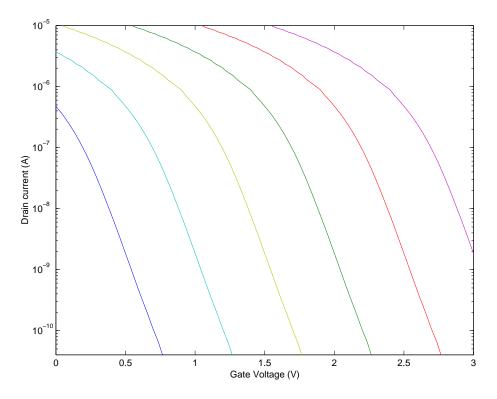

| Figure 13 | Layout, cross section, and circuit diagram of a floating–gate pFET                                   | 31   |  |  |  |

| Figure 14 | Traditional programmability achieved switchable arrays of elements                                   | 32   |  |  |  |

| Figure 15 | Drain curves for a single floating–gate transistor programmed over                                   |      |  |  |  |

|           | a range of currents                                                                                  | 34   |  |  |  |

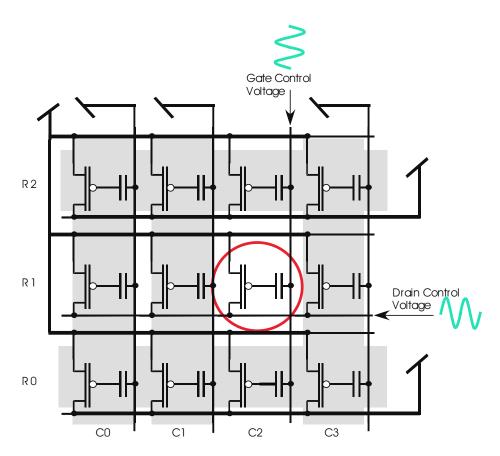

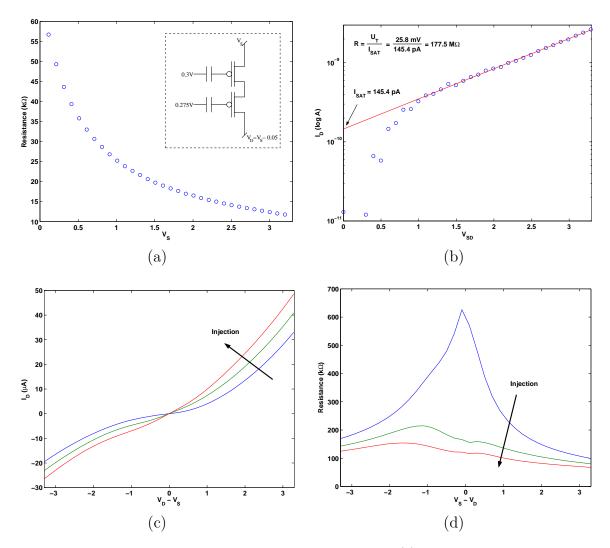

| Figure 16 | Array isolation technique used during programming                                                    | 35   |  |  |  |

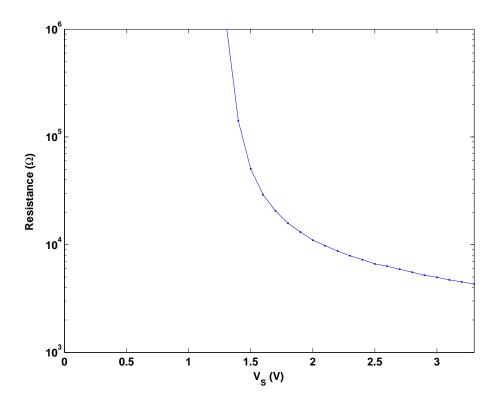

| Figure 17 | Resistance plot for a simple pFET switch                                                             | 36   |  |  |  |

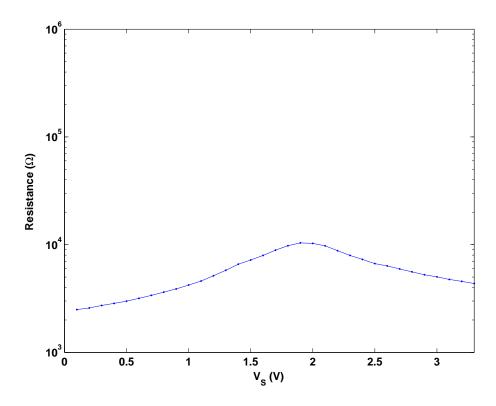

| Figure 18 | Resistance for a T–gate switch                                                                       | 37   |  |  |  |

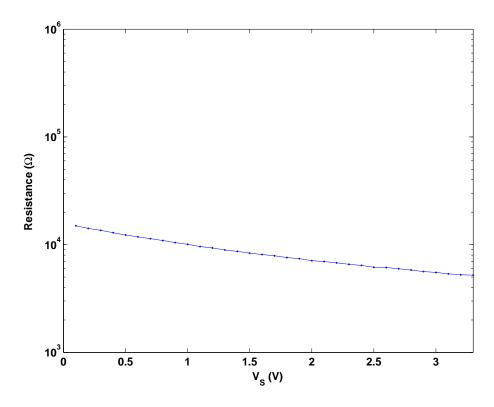

| Figure 19 | Resistance for a floating–gate switch                                                                | 39   |  |  |  |

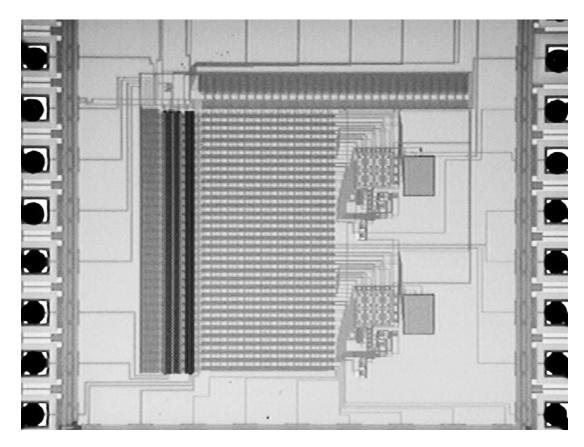

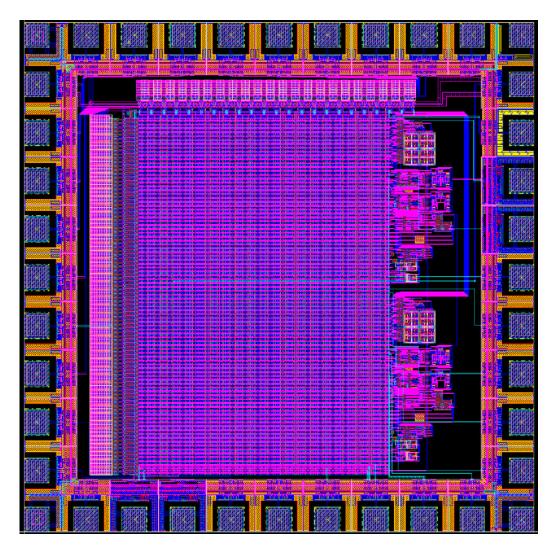

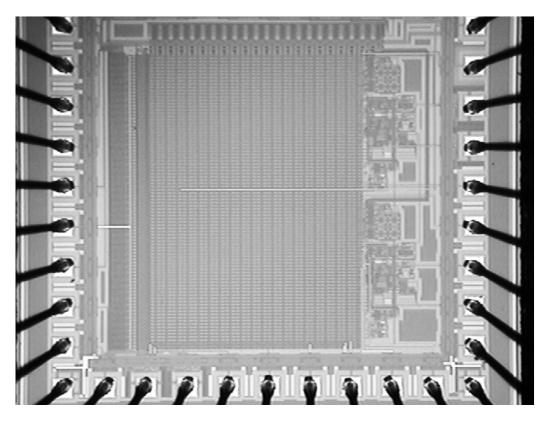

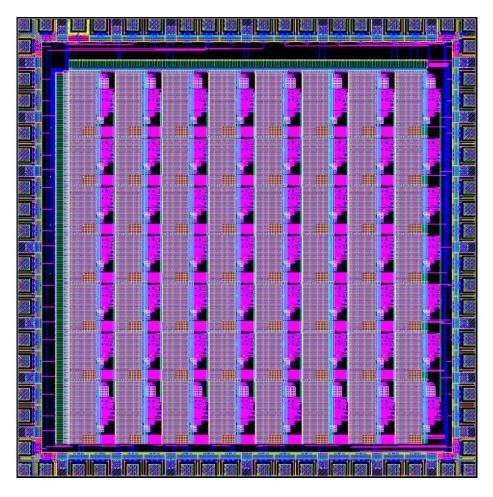

| Figure 20 | Die photo of the RASP 1.0 FPAA                                                                       | 41   |  |  |  |

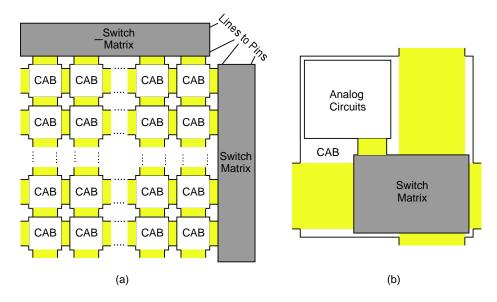

| Figure 21 | Block diagram of a generic FPAA chip                                                                 | 42   |  |  |  |

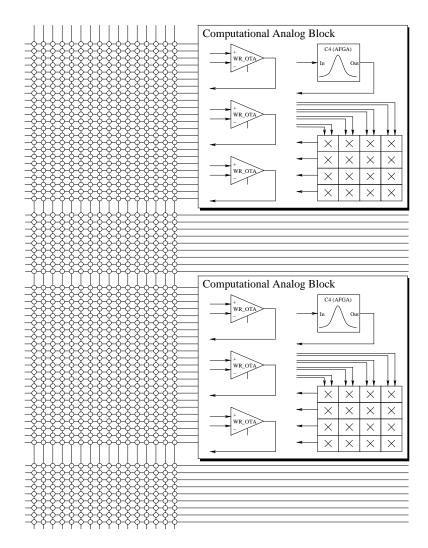

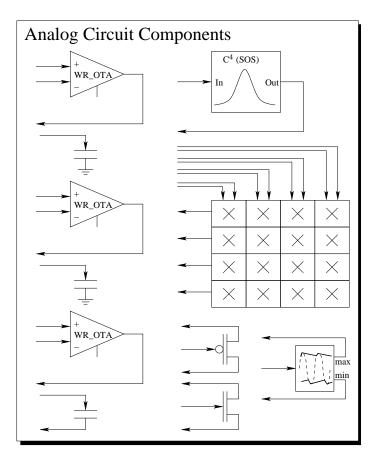

| Figure 22 | Computational Analog Block (CAB) components in the RASP 1.0                                          |      |  |  |  |

|           | FPAA                                                                                                 | 43   |  |  |  |

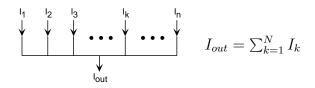

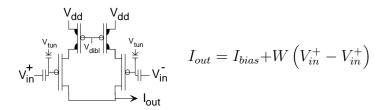

| Figure 23 | Current summing operation                                                                            | 44   |  |  |  |

|           | Multiplication operation                                                                             | 44   |  |  |  |

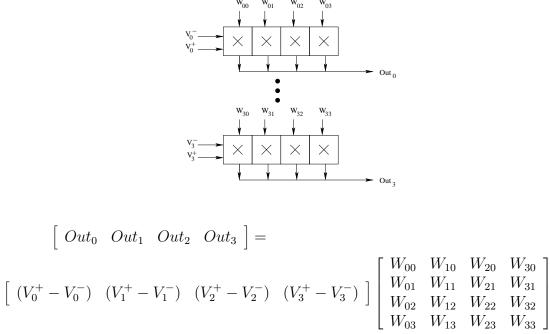

| Figure 25 | Vector–matrix multiplication operation                                                               | 45   |  |  |  |

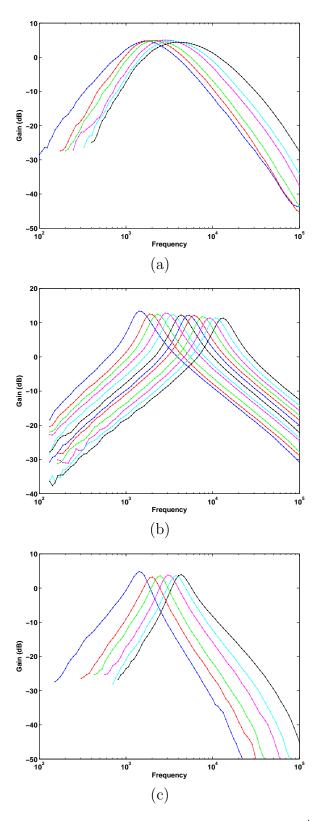

| Figure 26 | C <sup>4</sup> : RASP 1.0 bandpass filter circuit $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 46   |  |  |  |

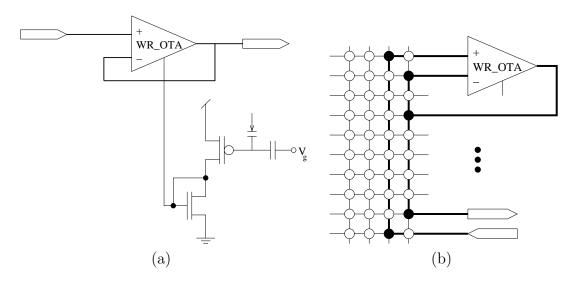

| 0         | Programming infrastructure                                                                           | 47   |  |  |  |

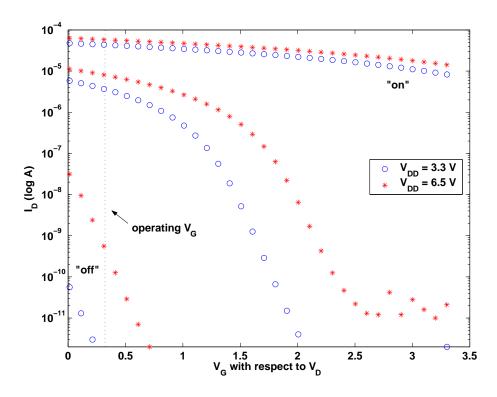

| Figure 28 | Floating–gate switch programmed across range from $off$ to $on$                                      | 49   |  |  |  |

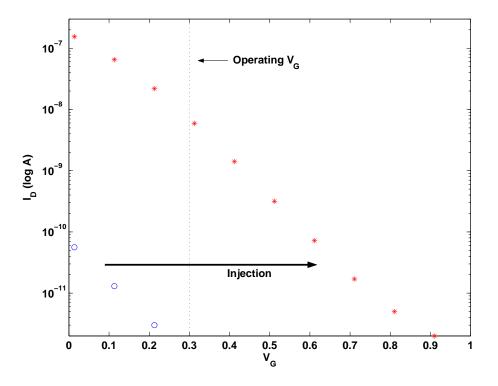

| Figure 29 | Switch characteristics of floating–gate transistors on RASP $1.0.$                                   | 51   |  |  |  |

| Figure 30 | Floating–gate transistor programming accuracy                                                        | 52   |  |  |  |

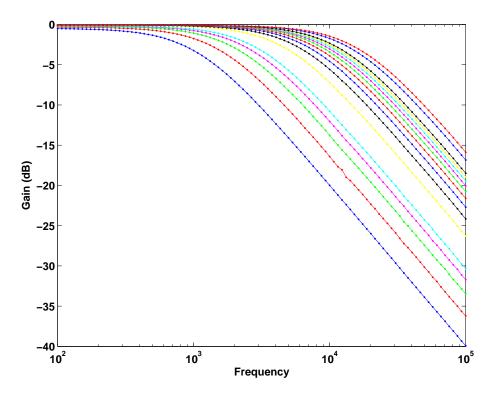

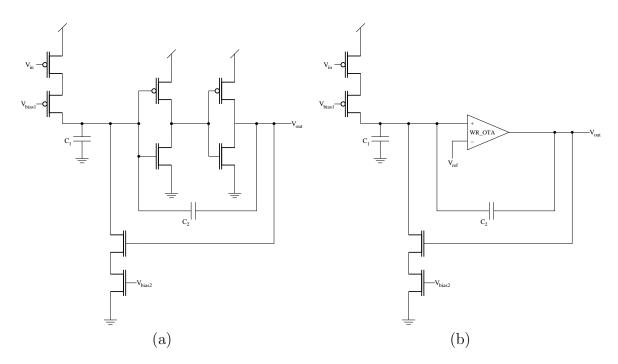

| Figure 31 | Integrator circuit diagrams                                                                          | 53   |  |  |  |

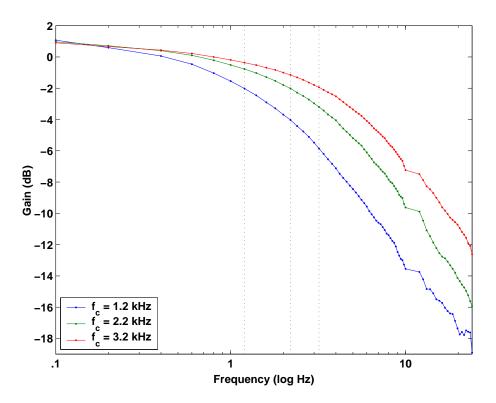

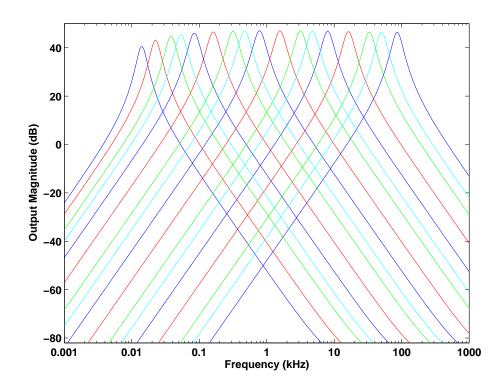

|           | Frequency response of the integrator circuit as implemented on RASP 1.                               | 0 54 |  |  |  |

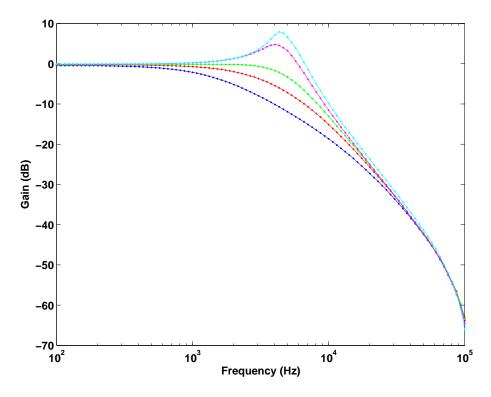

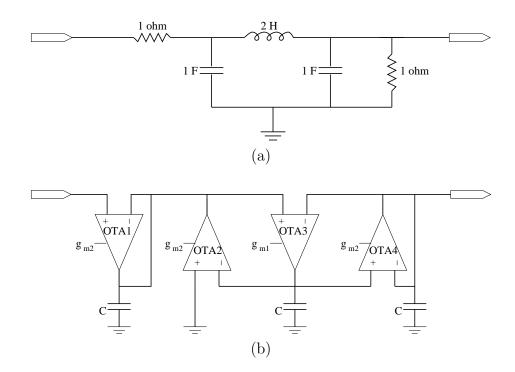

| Figure 33 | Second–order section circuit diagram                                                                 | 56   |  |  |  |

| Figure 34 | Simulated frequency response of the second–order section as imple-                                   |      |  |  |  |

|           | mented on RASP 1.0                                                                                   | 57   |  |  |  |

| Figure 35 | Frequency response of the second–order section circuits as imple-                                    |      |  |  |  |

|           | mented on RASP 1.0                                                                                   | 58   |  |  |  |

| Figure 36 | Simulation of frequency decomposition as implemented on RASP 1.0                                     | 58   |  |  |  |

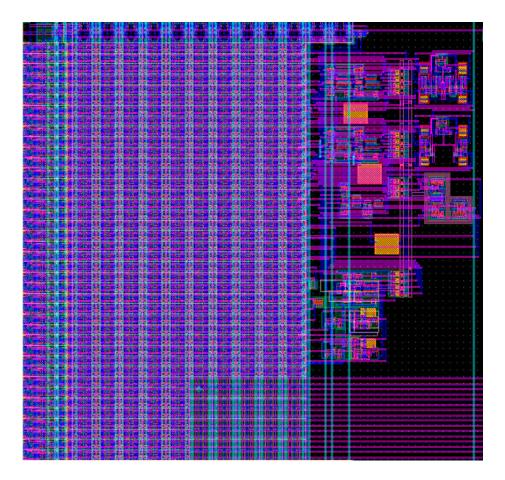

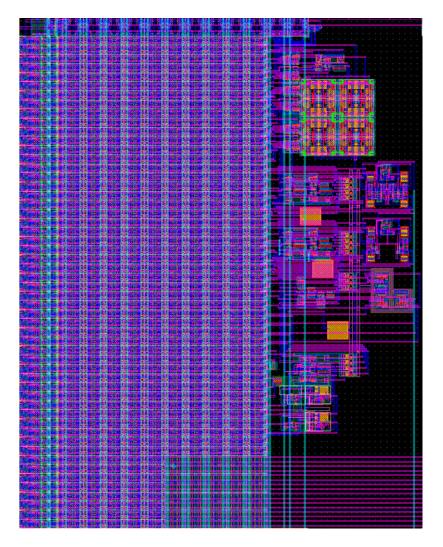

| Figure 37 | Top–level VLSI layout of the RASP 1.5 FPAA                             | 60    |  |

|-----------|------------------------------------------------------------------------|-------|--|

| Figure 38 | Die photo of the RASP 1.5 FPAA                                         |       |  |

| Figure 39 | Routing diagram of RASP 1.5                                            | 62    |  |

|           | CAB components on RASP 1.5                                             |       |  |

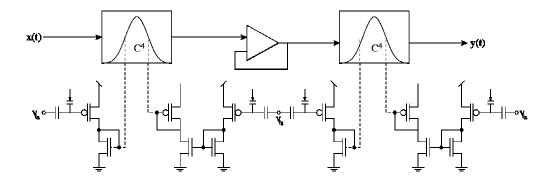

| Figure 41 | Block diagram of the $C^4$ second–order section on RASP 1.5            |       |  |

| Figure 42 | $C^4$ circuit used in the bandpass filter module on RASP 1.5           |       |  |

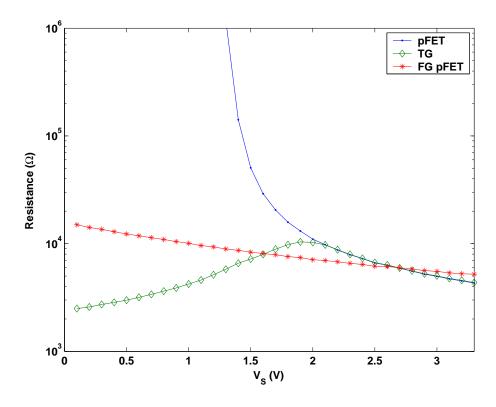

|           | Switch resistance on RASP 1.5 as compared to standard pFET and         |       |  |

|           | T-gate switches                                                        | 67    |  |

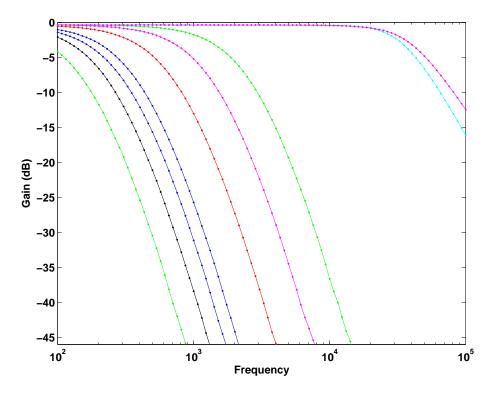

| Figure 44 | Integrator circuit diagrams                                            | 68    |  |

| Figure 45 | Frequency response of the integrator circuit as implemented on RASP 1. | .5 69 |  |

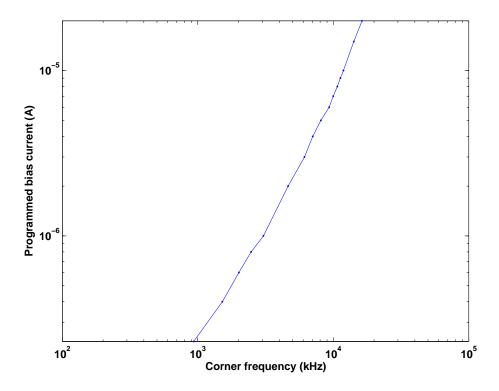

| -         | Correlation of integrator's bias current with its programmed corner    |       |  |

|           | frequency                                                              | 70    |  |

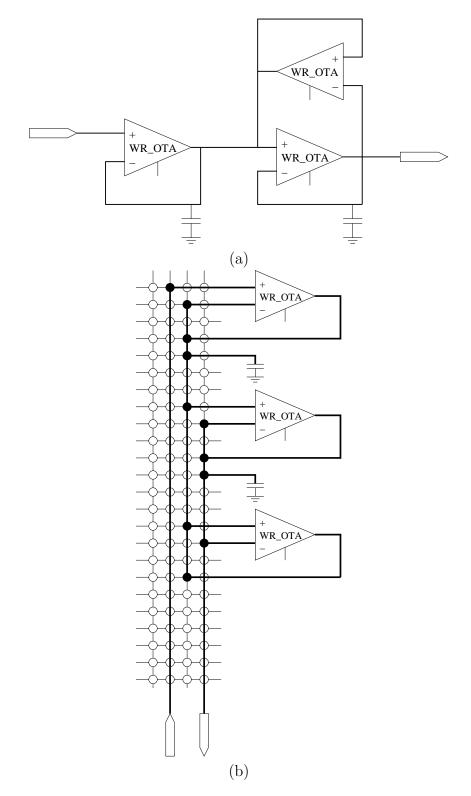

| Figure 47 | Second–order section circuit diagrams                                  | 71    |  |

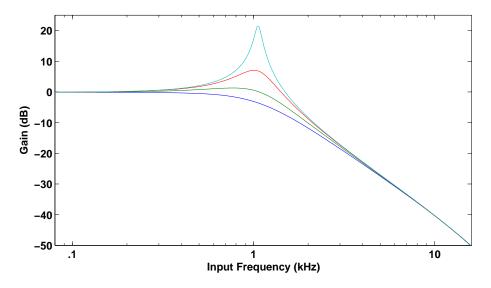

| Figure 48 | Frequency response of the second–order section circuit as imple-       |       |  |

| 0         | mented on RASP 1.5                                                     | 72    |  |

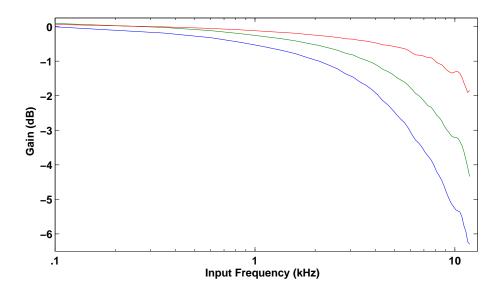

| Figure 49 | Third–order ladder filter circuit diagrams                             | 73    |  |

| Figure 50 | Frequency response of the third–order ladder filter circuit            | 74    |  |

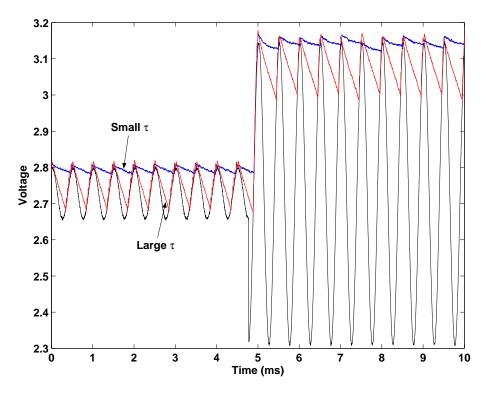

| Figure 51 | Output of the peak detector component for different time constants     | 75    |  |

| Figure 52 | Frequency response of the $C^4$ second–order section circuit as imple- |       |  |

|           | mented on RASP 1.5                                                     | 76    |  |

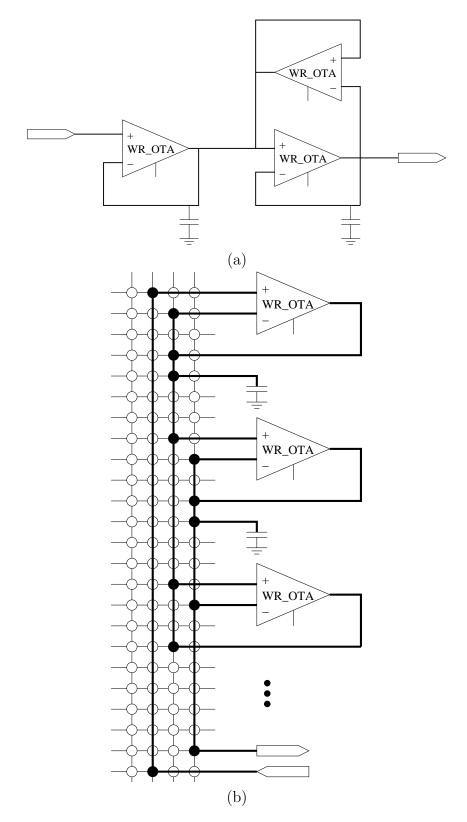

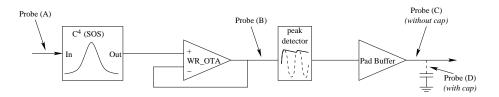

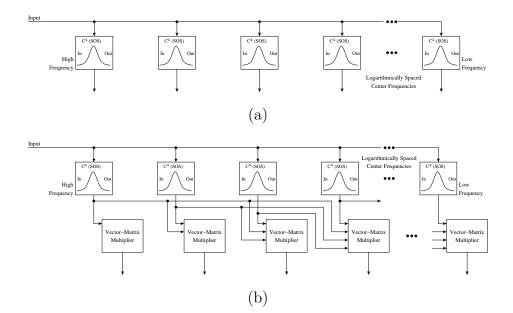

| Figure 53 | Circuit diagram of a typical subband system                            | 77    |  |

| -         | Experimental waveforms from the subband system                         | 78    |  |

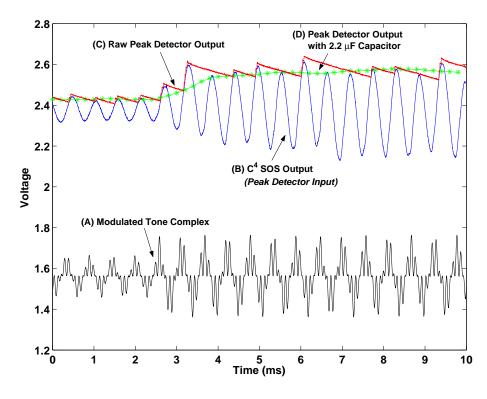

| Figure 55 | Circuit diagram and experimental results for a system with multiple    |       |  |

|           | subbands                                                               | 79    |  |

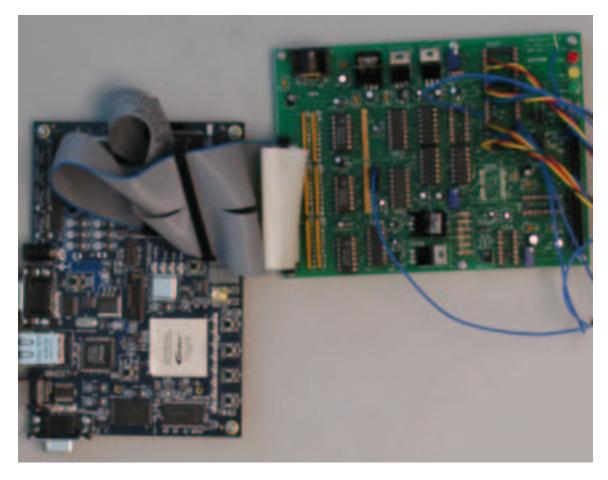

| Figure 56 | Picture of the mixed-signal prototyping platform                       | 81    |  |

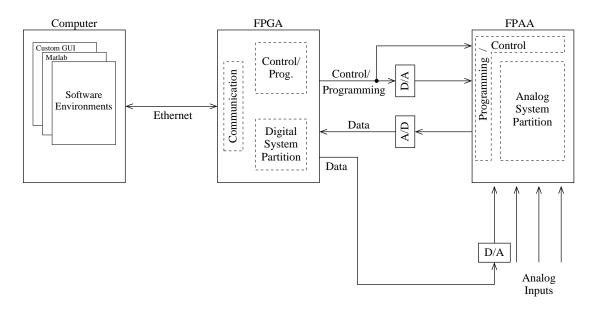

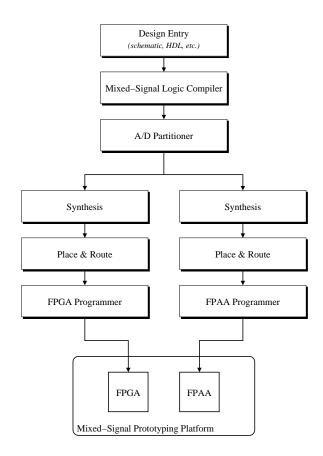

| Figure 57 | Block diagram of the mixed-signal prototyping system                   | 82    |  |

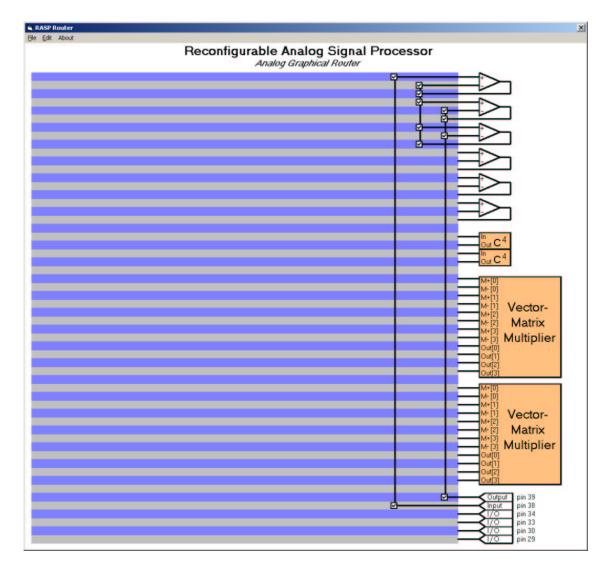

| Figure 58 | Screen capture of the graphical configuration software                 | 84    |  |

| Figure 59 | Screen capture of the graphical configuration software with a second-  |       |  |

|           | order section circuit being entered                                    | 86    |  |

| Figure 60 | Sample netlist output from the graphical FPAA configuration software   | 87    |  |

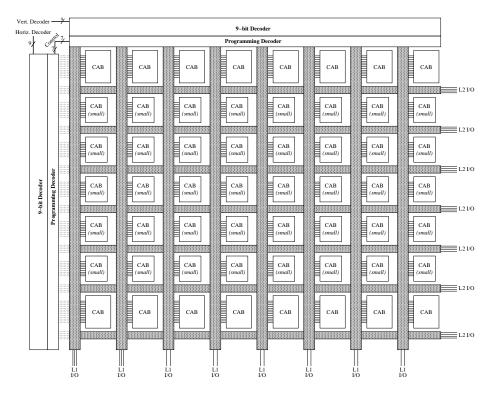

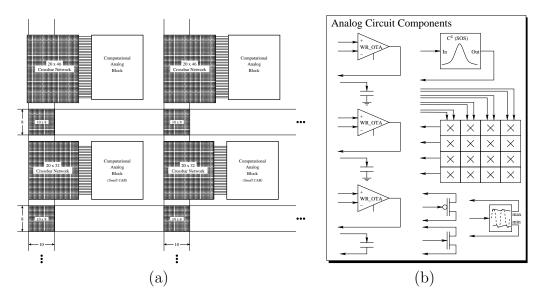

| Figure 61 | Top–level block diagram of the RASP 2.5 FPAA                           | 90    |  |

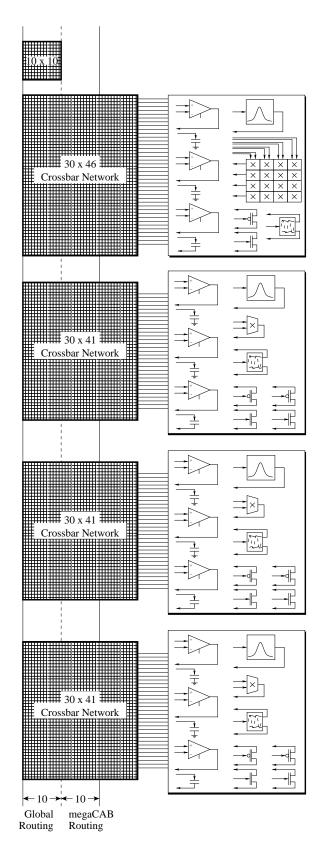

| Figure 62 | Block diagram of the routing and CAB architectures of RASP $2.5$ .     | 91    |  |

| Figure 63 | Top–level VLSI layout of RASP 2.5                                      | 92    |  |

| Figure 64 | VLSI layout of the small CAB on RASP 2.5                               | 93    |  |

| Figure 65 | VLSI layout of the full CAB on RASP 2.5                                | 94    |  |

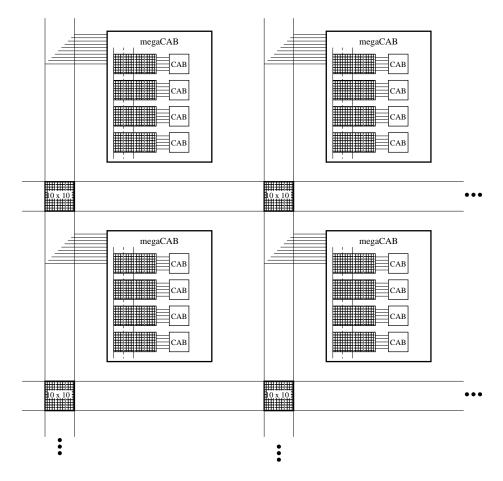

| Figure 66 | Routing architecture of FPAAs with hundreds of CABs                    | 95    |  |

| Figure 67 | megaCAB architecture                                                   | 96    |  |

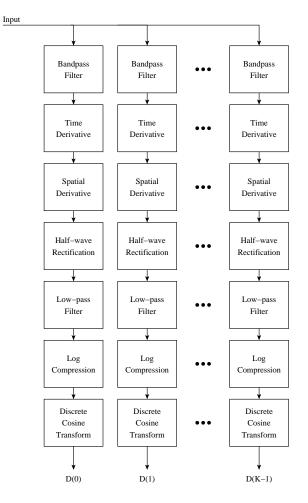

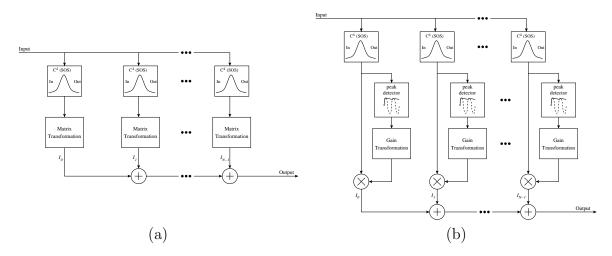

| Figure 68 | Feature extraction system diagram                                      | 98    |  |

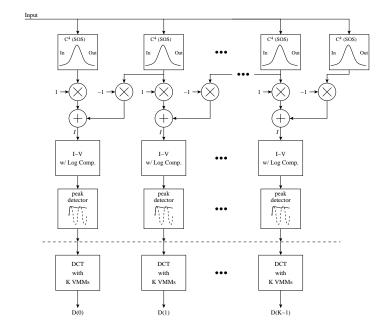

| Figure 69 | First–order difference equation implementation                         | 98    |  |

| Figure 70 | FPAA synthesis of the feature extraction algorithm                     | 99    |  |

| Figure 71 | Generalized block diagrams for typical audio processing synthesis .    | 100   |  |

| ~         |                                                                        | 101   |  |

| Figure 73 | Block diagrams for example cochlea models                              | 102   |  |

| Figure 74 | Ideal computer-aided design (CAD) tool flow for large-scale FPAAs      | 104   |  |

#### SUMMARY

Field–programmable analog arrays (FPAAs) provide a method for rapidly prototyping analog systems. Currently available commercial and academic FPAAs are typically based on operational amplifiers (or other similar analog primitives) with only a few computational elements per chip. While their specific architectures vary, their small sizes and often restrictive interconnect designs leave current FPAAs limited in functionality, flexibility, and usefulness. Recent advances in the area of floatinggate transistors have led to an analog technology that is very small, accurately programmable, and extremely low in power consumption. By leveraging the advantages of floating-gate devices, a large-scale FPAA is designed that dramatically advances the current state of the art in terms of size, functionality, and flexibility. A largescale FPAA is used as part of a mixed-signal prototyping platform to demonstrate the viability and benefits of cooperative analog/digital signal processing. This work serves as a roadmap for future FPAA research. While current FPAAs can be compared with the small, relatively limited, digital, programmable logic devices (PLDs) of the 1970s and 1980s, the floating-gate FPAAs introduced here are the first step in enabling FPAAs to support large-scale, full-system prototyping of analog designs similar to modern FPGAs.

#### CHAPTER 1

### **RAPID PROTOTYPING OF ANALOG SYSTEMS**

The process of designing, fabricating, and testing an analog chip requires certain expertise and is often long and expensive. As shown in Fig. 1, the process is not unlike designing digital ASICs (application–specific integrated circuits), except that there are fewer tools and libraries available to the designer. The traditional analog design cycle often requires several iterations of the fabrication process, which with the simulation, VLSI layout, and testing phases can easily consume a year or more for typical IC designs. However, the use of a reconfigurable analog chip, dubbed a field– programmable analog array (FPAA), would dramatically reduce the design cycle by removing the fabrication stage from the iterative process. Thus, many designs may be tested and modified within a single day.

Like field–programmable gate arrays (FPGAs), FPAAs are not optimal for all solutions. They are, however, very useful for many situations, and a solution can be found for many problems not requiring full functionality. Relative to custom–designed analog circuits, a design implemented on an FPAA results in higher parasitics as well as increased die area for a given design; therefore, the design always possesses some inefficiencies (i.e., lower bandwidth and higher consumed power). On the other hand, since analog circuit design is often time–consuming, these adverse characteristics are well balanced by markedly decreased time to market.

FPAAs have been of interest for some time, but historically, these devices have had very few programmable elements and limited interconnect capabilities, making them limited in their usefulness and versatility. The next–generation FPAA needs to correct these problems in order to extend the usefulness and acceptance of FPAAs. As shown in Fig. 2, traditional FPAAs resemble the early PLDs in that they are focused on small systems such as low–order filtering, amplification, and signal conditioning. However,

#### **Traditional Analog Design Cycle:**

**Figure 1.** This figure illustrates the advantages of designing analog ICs using an FPAA–based rapid prototyping technology as opposed to the traditional design cycle of VLSI layout and fabrication. The traditional analog design cycle often requires 3 or more iterations of the fabrication process which extends the development process to over a year. With an FPAA–based system, designs can be synthesized, tested, and modified 20 or more times within a matter of days instead of years.

the class of large–scale FPAAs that we are exploring here are more analogous to modern FPGAs. These FPAAs are much larger devices with the functionality needed to implement high–level system blocks such as programmable high–order filtering, Fourier processing, and signal analysis in addition to having a large number of fine– and medium–grain, programmable analog blocks (e.g., operational transconductance amplifiers (OTAs), transistor elements, capacitors, etc.).

#### 1.1 Low–Power Signal Processing

The future of FPAAs lies in their ability to speed the implementation of advanced, low-power signal processing systems. In this thesis, an FPAA architecture is presented for achieving flexible, large-scale FPAAs targeted at mainstream signal processing systems. These FPAAs are intended to impact analog signal processing in two ways: first, they perform the function of all rapid prototyping devices in reducing development time. Second, they are a platform for implementing advanced signal processing functions—usually realized only in digital systems—with analog circuits.

Figure 2. (a) Digital PLDs can be used to implement small, carefully defined pieces of a complex system, while FPGAs can be used to implement entire systems including processor datapaths, complex DSP functions, and more. Modern FPGAs can be 100 - 10,000 times larger and more complex than the PLDs of the 1970s and 1980s. (b) Analagously, traditional FPAAs resemble the early PLDs in that they are focused on small systems such as low–order filtering, amplification, and signal conditioning. However, the FPAAs based on floating–gate devices presented here are much larger devices with the functionality needed to implement high–level system blocks such as programmable high–order filtering and Fourier processing in addition to having a large number of programmable op–amp and transistor elements.

The primary benefit of implementing analog signal processing systems is the potential for large savings in power consumption. For digital signal processing (DSP) microprocessors, Gene's law postulates that the power consumption, as measured in milliwatts per million multiply–accumulate (mW/MMAC) operations, is halved about every 18 months, as shown in Fig. 3 [28]. These advances largely follow Moore's law, and they are achieved by using decreased feature size, intelligent clock gating, and other refinements. Unfortunately, a problem looms on the horizon; the power consumption of the analog–to–digital (A/D) converter does not follow Gene's law and will soon dominate the total power budget of digital systems. While A/D–converter resolution has been increasing at roughly 1.5 bits every five years, the power performance has remained the same, and soon, physical limits will further slow progress.

For analog systems to be desirable to the largely DSP–oriented community, they not only need to have a significant advantage in terms of size and power, but

Figure 3. Data from [28] showing the power consumption trends in DSP microprocessors along with data taken from a recent analog, floating–gate integrated chips developed by the CADSP team [13, 22, 47, 51, 77].

they must also be relatively easy to use and easily integrated into a larger digital system. In addition, they must be shown to be accurately programmable and effective at implementing many of the key systems found within DSP. As shown in Table 1, the functionality desired for any technology focused on signal processing includes monolithic filters, linear and nonlinear scalar functions, vector-matrix operations (i.e., transforms, distance metrics, winner-take-all, principle component analysis, etc.), linear-phase filters, adaptation, and tap delay lines for FIR systems.

### 1.2 Cooperative Analog/Digital Signal Processing

This thesis is part of a larger effort within the Cooperative Analog/Digital Signal Processing (CADSP) group at the Georgia Institute of Technology. The goal of the CADSP group is to investigate the partitioning of signal processing systems between

| Functionality               | DSP $\mu$ P | Trad.<br>Analog | Large–scale<br>FPAA |

|-----------------------------|-------------|-----------------|---------------------|

| Programmable                | •           |                 | •                   |

| Monolithic Filters          | 0           | •               | •                   |

| Linear Scalar Operations    | •           | 0               | •                   |

| Nonlinear Scalar Operations | 0           | •               | •                   |

| Vector–Matrix Operations    | 0           | 0               | •                   |

| Linear–phase Filters        | •           | —               | 0                   |

| Adaptivity                  | 0           | _               | 0                   |

| Tap Delay Lines             | •           | 0               | 0                   |

Key:

- = No or very limited support

$\circ = \mathrm{Possible}$

$\bullet$  = Efficient, well–suited to technology

Table 1. Summary of Signal Processing Functionality

the analog and digital domains. Most current signal processing systems that generate digital output place the ADC as close to the analog input signal as possible to take advantage of the computational flexibility available in digital processors (see Fig. 4). However, the development of large-scale FPAAs—and the CAD tools needed for their ease of use—would allow engineers the option of performing some of the computations in reconfigurable analog hardware prior to the analog–to–digital (A/D)converter, resulting in both a simpler A/D converter and a substantially reduced computational load on the digital processors that follow. By leveraging the power efficiencies mentioned in the previous section, some analog signal processing systems have been shown to achieve as much as five orders of magnitude over typical DSP microprocessor implementations [5, 22, 77]. As illustrated in Fig. 3, this corresponds to a 20 year leap forward on the power curve predicted by Gene's law [37]. Additionally, the output of such an analog system can be higher-level information, such as Fourier coefficients or phonemes of speech. This information can potentially be converted into the digital domain with a much lower resolution and/or conversion speed than would be needed in the traditional system where a literal sampling of the incoming

**Figure 4.** In most traditional digital signal processing systems, the analog–to–digital converter (ADC) is placed as close to the real–world, analog inputs as possible. However, significant power savings can be achieved by moving some of the signal processing functionality into the analog domain (in front of the ADC). Conceptually, this analog signal processing can be combined with the ADC to form a "specialized ADC" as shown here.

signal is needed [45]. Thus, a simpler and much smaller A/D converter can be used.

As an example of the advantages of moving the A/D boundary, one can consider a software radio system. In the traditional implementation, the analog signals coming from multiple (e.g., four to eight) antennas must each be converted to the digital domain. The signals coming from the antennas are still modulated by the carrier frequency, and thus, multiple high–speed A/D converters must be used. In a CADSP system, however, the demodulation and beam–forming functions can be implemented in floating–gate analog circuitry [41, 45, 51, 63]. The output from the analog domain is then a single, baseband signal that can be converted using a much slower A/D converter.

To realize the power savings of analog systems in advanced signal processing systems, the CADSP group focuses on the use of floating–gate devices as the enabling technology. Recent advances in floating–gate circuit technology have yielded promising results in the implementation of complex analog signal processing systems. Floating–gate circuits have already been demonstrated in the areas of noise suppression, speech processing, image processing, and adaptive systems [6, 20, 23, 39, 47, 77, 81]. Work has also progressed on creating fast, accurate methods of programming large arrays of floating–gate transistors [76]. This is an important factor in determining the viability of using floating–gate devices in large, complex systems, particularly in mass–production environments.

The CADSP group brings together researchers from three areas of electrical engineering: analog circuit design, digital signal processing, and computer/systems engineering. Within the group, the analog circuit designers focus on the development, characterization, and testing of low–level floating–gate circuits as the core technology of CADSP systems. The digital signal processing researchers focus on the algorithmic translation of digital signal processing systems into the analog domain. They are particularly interested in capitalizing on the large–scale system parallelization that is possible within the analog domain, as well as the real–time, continuous–flow nature of analog systems and its affect on traditional algorithms. Finally, the computer engineering researchers focus their attention on the system–level development of the hardware systems and computer–aided design (CAD) tool flows necessary to realize practical CADSP systems.

This thesis falls within the computer engineering sub-area of the CADSP group. As a practical matter, the investigation of a reconfigurable system for rapidly prototyping analog and digital systems is extremely important in moving the CADSP effort forward. To date, there are no large–scale FPAAs available that will allow designers to test complex analog and mixed–signal systems. Furthermore, given the programmable nature of floating–gate devices, the development of FPAAs based on this core technology is a natural and important step toward the realization of a widely accessible method of creating analog and mixed–signal designs. FPAAs will provide a platform for exploring cooperative analog/digital signal processing systems that optimally balance the low–power, real–time computational nature of analog circuits with the flexibility and robustness of digital systems.

## CHAPTER 2 HISTORY AND MOTIVATION

Reconfigurable hardware has long been of interest to circuit designers and engineers. In the digital domain, programmable logic devices (PLDs) have made a large impact on the development of custom digital chips by enabling a designer to try custom designs on easily reconfigurable hardware. Since their conception in the late 1960s and early 1970s, PLDs have evolved into high–density field–programmable gate arrays (FPGAs) [9, 14, 80]. Modern FPGAs are widely used in the laboratory for rapidly prototyping digital hardware, as well as in production goods to decrease time-tomarket and to allow products to be easily upgraded after being deployed.

In the analog domain, however, progress has been much slower. While early analog integrated circuits (ICs) were often tunable with adjustable biases, truly reconfigurable analog circuitry in the form of field–programmable analog arrays (FPAAs) did not emerge until the late 1980s [35, 75], and commercial offerings did not reach the market until 1996 [61].

#### 2.1 Background on FPAAs

FPAAs can be broadly classified into two categories: continuous-time devices and discrete-time devices [33]. There are academic and commercial examples of both categories, as well as advantages unique to each design methodology. This section will focus more on continuous-time FPAAs, because the large-scale FPAA architecture developed herein is a continuous-time FPAA; however, previous work on discrete-time FPAAs will be summarized for comparison sake. Previous FPAAs have varied greatly in terms of computational granularity and capability, interconnect structure, performance, and application focus.

Fundamentally, FPAAs include two functions: routing and computation. (The

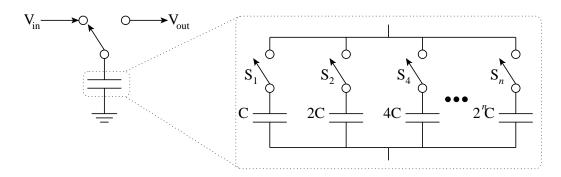

Figure 5. Most discrete-time FPAAs use switched-capacitor designs. As the switch momentarily rests on the  $V_{in}$  terminal, the input voltage charges the capacitor. Then the switch moves to the  $V_{out}$  terminal where it is discharged through the next phase of circuitry. The programmability within switched-capacitor designs is usually achieved using an array of appropriately sized capacitors. Thus, the effective capacitance at each switch can be varied by setting the *n* digital memory cells controlling switches  $S_1$  to  $S_n$ . In essense, this capacitor bank is equivalent to having a Digital-to-Analog Converter (DAC) being included in each computational block.

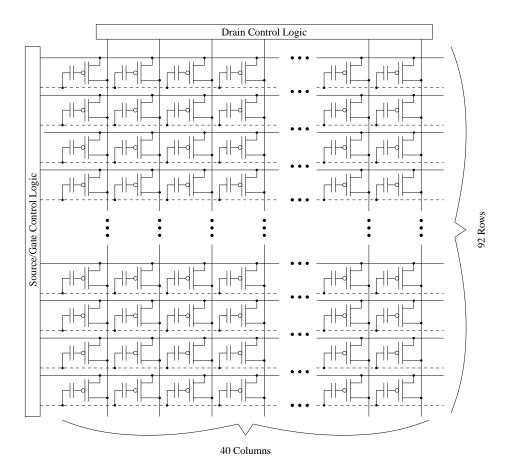

next section will show that some designs combine these two functions into a single unit; however, both elements are still present whether explicitly or implicitly.) The routing elements are typically networks of switches connected together by signal lines with the network architecture and switch types varying dramatically across different FPAAs. The switch networks then connect to the computational elements of the system. If there is more than one type of computational element, the computational elements are usually grouped together to form a computational analog block (CAB) that is analagous to the computational logic blocks found on FPGAs. If there is only one type of computational element, the element and the CAB are one and the same; however, for convenience, the computational elements will still be referred to as CABs here.

#### 2.2 Discrete-time FPAAs

Discrete-time FPAAs are typically switched-capacitor designs. For these circuits, the incoming voltage is sampled by opening and closing a switch that connects the input to an initial capacitor (Fig. 5). The switch and capacitor form a type of analog register, and the system's signal path is partitioned by these registers. The basic computational

|        | Typical<br>Computational |                              |                        |

|--------|--------------------------|------------------------------|------------------------|

|        | Elements                 | Advantages                   | Disadvantages          |

| Fine   | Transistors              | Small                        | Large $\#$ of switches |

|        |                          | Simple CAB design            | Large parasitics       |

|        |                          | Generic building blocks      |                        |

| Medium | Op-amp                   | Semi-generic building blocks | Limited size           |

|        | OTA                      | Moderate CAB design          | Severe functionality / |

|        | Current conveyor         | Large variety of CAB /       | performance trade–off  |

|        |                          | interconnect designs         |                        |

| Coarse | Fourier Processor        | Higher performance           | Limited flexibility    |

|        | "Expert cell"            | Easier user interface        | Limited functionality  |

**Table 2.** Summary of FPAA Granularity: The granularity of the computational logic used in an FPAA impacts the size, performance, flexibility, and functionality of the device.

elements are usually operational amplifiers and analog registers, which synthesize a linear resistor whose value is determined by the switching rate and capacitor value. The synthesis of linear variable resistors gives switched–capacitor FPAAs greater flexibility than traditional continuous–time FPAAs; however, they can also be harder to design proficiently, because the switches and capacitors can introduce noise and nonlinearities into the system that must be overcome [61]. In addition, these designs have a limited bandwidth based on the sampling rate, are complicated by the need for continuous–time anti–aliasing and reconstruction filters at the input and output, and can be large if programmable capacitor arrays are included [35, 61].

In the late 1990s, several switched–capacitor FPAAs were introduced by both academic and commercial entities. In the academic arena, basic computational elements vary from the simple operational amplifier [21, 50] to the more complex blocks, such as a lossless integrator and lossy integrator connected in a loop [53]. These devices also can have programmable capacitor and/or programmable resistor arrays, which add programmability [21, 35]. In the commercial arena, Motorola was one of the first companies to bring a general–purpose FPAA to market with their MPAA020 and MPA1000 series [4, 10, 61]. Since then, a spin–off company named Anadigm has marketed these switched–capacitor FPAAs [2]. The newest Anadigm devices have CABs with two differential operational amplifiers, programmable capacitor banks, a successive approximation register (for implementing an A/D converter), and a high– speed comparator [3]. However, even the latest devices are relatively limited with only four CABs per chip and are targeted at basic signal conditioning and filtering applications.

Switched–capacitor designs are not the only discrete–time FPAAs. Switched– current circuits can also be used to build an FPAA. The advantages of this technique include not requiring operational amplifiers, capability of fabrication on standard digital CMOS processes, and elimination of distortion on the signals due to parasitic resistances. To their detriment, these designs can produce less accuracy than switched–capacitor circuits, and since the signals are all currents, a given output stage can drive only one input stage [12].

#### 2.3 Continuous-time FPAAs

Continuous-time FPAAs typically use an array of fixed components (often operational amplifiers and/or transistors) that are interconnected by a switching matrix. The switches are usually controlled by digital registers, which can be loaded by an external controller, thus allowing the FPAA to be configured to implement a number of different designs. This type of FPAA is advantageous because potential sampling artifacts are avoided; anti-aliasing filters are not needed; common, relatively easy design processes can be used (e.g., standard CMOS processes); and large signal bandwidths can be supported with predictable performance [61]. However, the switching networks introduce parasitic impedances into the signal path that limit the bandwidth and add noise to the system. Some of the literature has focused on minimizing the number of switches in the signal path, but this can severely limit the flexibility of the FPAA [24, 55, 58, 67].

#### 2.3.1 Computational Granularity and Capability

The granularity of the computational logic that forms the basis of the FPAA's design is an important design characteristic. As summarized in Table 2, the finest– grain architectures typically use transistors as the core computational cell. While these designs offer the most flexibility and generality, synthesizing a sufficiently complex system requires a large number of transistors to be wired together. Thus, a large number of switches are introduced into the signal path. The switch parasitics and finite resistance increases the noise within the system and limits the performance/bandwidth [24, 49, 67]. Fine–grain FPAAs have been primarily relegated to research in evolvable hardware [48, 72, 78], where the lowest–level building blocks are desirable for generating unique designs using non-traditional design methodologies. Systems that are designed using genetic algorithms are not as negatively affected by the parasitics and non-ideal resistances of switches, since these parameters are taken into account and even exploited throughout the evolutionary design process.

On the coarse–grain extreme, one finds FPAAs such as IMP's EPAC devices, which contain an "expert cell" as the core computational block [49]. In the IMP50E10 device, this cell is a very high–level block with limited interconnects that is aimed directly at signal conditioning applications. The logic within the cell can be configured to function as an amplifier with an optional low–pass filter or as a comparator with optional hysteresis. There is also a dedicated D/A converter for defining the reference point for the comparator. These coarse–grain designs sacrifice flexibility and generality in favor of increased, more predictable performance [49].

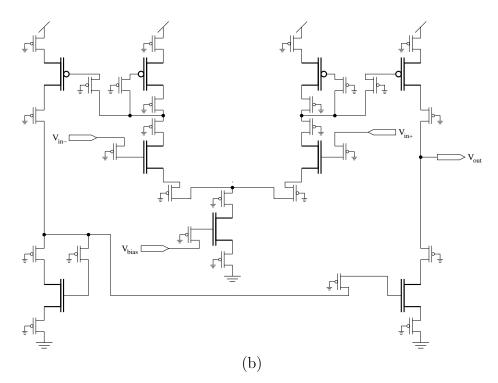

The majority of FPAAs fall in-between these two extremes. A number of FPAAs use an operational transconductance amplifier (OTA) as the basic computational element [26, 64, 65, 67, 70, 71]. OTAs work well as the core computational cell, because their transconductance can be programmed either by varying the analog bias voltage or by changing the gain of the output current mirrors [1, 65]. In addition, it has been shown that OTAs can implement a wide range of linear and nonlinear circuits. Several FPAA designs have focused on synthesizing linear circuits and use OTAs to implement amplification, integration, and filtering functions [64, 65, 67]. Ray et al. have proposed a more generalized scheme in which linear circuits are synthesized using an OTA-based lossless integrator and an OTA-based lossy integrator as the basic functional blocks. They also use an OTA-based multiplier and OTA-based integrator as the basic functional block for synthesizing nonlinear circuits such as amplitude and frequency modulation [70]. Sanchez-Sinencio et al. have used OTAs to implement nonlinear functions such as multiplication, division, square root, exponentiation, and piece-wise linear operations [71].

Similiarly, several FPAA designs have been proposed using a current–conveyor structure as the basic building block. Current conveyors are similar to OTAs; however, when used as an amplifier they exhibit a constant bandwidth that is independent of gain. They also do not require compensation circuitry to insure stability, and thus, they can operate at higher frequencies [34]. Gaudet et al. have proposed a current– conveyor based FPAA in which each CAB contains a second–generation current– conveyor, two programmable capacitors, and two programmable resistors (transconductors) [34]. This CAB is shown to implement amplification and first–order filtering functions, as well as log and anti–log functions with the addition of switchable diodes. Premont et al. also describe an FPAA based on current–conveyors [68]. The core cell includes tuneable resistors and a current–conveyor. It has been demonstrated that this cell can be configured to implement a tuneable capacitor, and thus is suitable for amplification and filtering functions.

Other medium–grain computational blocks have been used in FPAAs as well. Pierzchala et al. used an OTA–based amplifier/integrator cell that does not require switches in the signal path [67]. Quan et al. proposed a current–mode FPAA that uses a cascode current–mode integrator as the basic building block [69]. This core cell

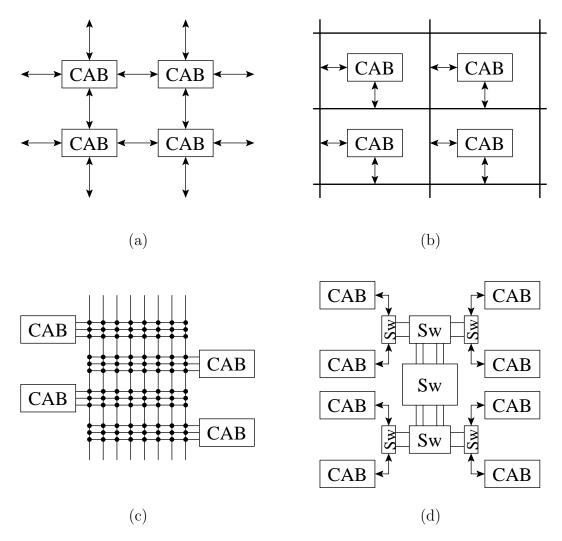

**Figure 6.** A number of different interconnect schemes have been used in FPAAs including (a) local connections, (b) global connections, (c) cross–bar networks, and (d) fat–tree interconnects.

can implement amplification, integration, and attenuation with a minimum number of switches in the signal path [24]. In a more specialized chip design for prototyping machine learning algorithms, Bridges et al. used a mix of components including transistors, a differential pair, a current mirror, a bias current source, and configurable capacitors [11]. They used these blocks to synthesize single learning primitives such as correlational learning, regression learning, and clustering.

#### 2.3.2 Interconnect Structure

Aside from CAB components, a number of different interconnect structures have also been proposed for FPAAs (see Fig. 6). The most common interconnect switch is a MOS transistor controlled by a digital memory [4, 12, 34, 55, 65, 69]. Unfortunately, switch resistance in these devices can range from 1000 to 5000  $\Omega$  making them a limiting factor in designing large, complex FPAAs [21]. Lee and Gulak used this type of pass–transistor switch in [55, 58]; however, the parasitic effects of these switches greatly limited the performance and capability of their FPAA [59]. As a result, they replaced the pass transistors with four–transistor transconductors, which increased the performance and functionality of their FPAA [56]. The new design reduced the parasitic effects, increased the linearity, and increased the noise immunity. In addition, a transconductor switch exhibits a linear resistance, thus each switch can also be used as a variable resistor by driving the gate voltage with a multi-valued memory (or another internal or external signal). However, the large transistors needed for low–frequency operation and the addition of a multi-valued memory for each switch greatly increases the area required for the interconnects [59].

Other switch designs have been proposed as well. Premont et al. used a current conveyor as the switching element [68]. This was particularly novel, because they used the current conveyor for both the switching element and the active computational element. In an effort to provide a radiation-tolerant FPAA for space applications, Edwards et al. proposed the use of metal-to-metal antifuses for the switches [21]. The antifuse design they used also has the benefit of a relatively low resistance (in the 15 to 25  $\Omega$  range).

In addition to using different switches, interconnect schemes have also varied in overall architecture. In the Premont et al. FPAA previously mentioned [68], the use of a current conveyor for both the switching element and active computational element results in CABs and switching interconnects that are indistinguishable from one

another. The overall architecture becomes a homogeneous mesh of logic with a minimum number of switches introduced into the signal path. Various other approaches have also been tried in an effort to minimize the number of switches. Quan et al. proposed the use of local interconnects. In their architecture, each CAB can be connected to its eight neighbors and itself [24]. This would seem to be a severe limitation on the flexibility of this FPAA; however, they focus on the large number of analog circuits with mostly local interconnections [69]. A similar idea was proposed by Becker et al. [7]. They used digitally tunable transconductors as the computational element. In this design, CABs were arranged in a hexagonal pattern; each CAB consists of seven programmable transconductors—six for connecting to each neighboring CAB and one for local feedback. This FPAA is designed for implementing Gm–C filters (with the required capacitance being provided by the parasitic impedance of the transconductors). Again, the lack of dedicated routing hardware is a limiting factor in this design, but if the target applications are constrained to be Gm–C filters, it is satisfactory. Pierzchala et al. tried an even more limiting architecture in which no electronic switches were included in the signal paths [67]. While these designs may provide benefits in bandwidth and signal-to-noise ratio (SNR), they lack the flexibility and generality needed in a truly general-purpose FPAA.

In another design, Pierzchala et al. introduced an interconnect scheme with both local and global signal paths [66]. This configuration provided local routing paths for a cell's four neighbors (north, south, east and west), as well as connections to global busses that run horizontally, vertically, and diagonally. This two-tiered hierarchy increases the routing flexibility within the FPAA. An even more flexible interconnection network is the crossbar switch [70]. The crossbar switch offers a nonblocking, fully connectable architecture; however, for a large number of inputs and outputs its size can be too big  $(O(N^2)$  growth rate) [55]. Lee and Gulak tried to solve this problem by using an area-universal fat-tree network [58]. They used a heirarchical fat-tree network of small crossbar switches where the CABs were connected as the leaves of the tree. In an additional effort to minimize the size required by the switch networks, the number of connections was constrained [55]. Unfortunately, their prototype was too small to fully test this interconnect concept.

#### 2.4 Complimentary Research

There are several areas of research progressing in fields complimentary to FPAAs. On the hardware side, there are different attempts at combining programmable digital and analog hardware. Chow et al. have proposed a single–chip field–programmable mixed–analog–digital array (FPMA) for prototyping mixed–signal systems [15]. This effort combines an array of standard digital FPGA cells with a programmable array of operational amplifiers, capacitors, resistors, and diodes [16]. The reconfigurable analog hardware is limited in nature and is not the primary emphasis in this case. Instead, the focus of this work is on configurable A/D and D/A converters that reside between the blocks. Lee has also done some work in this area; however, his focus is also on the design of reconfigurable A/D and D/A converters and not the design of complex analog arrays [57].

Faura took a slightly different approach to the FPMA concept by combining digital FPGA logic, programmable analog logic, and a digital microcontroller on the same integrated circuit (IC) [27]. Once again, the reconfigurable analog hardware was not very complex. In this case, the analog circuitry was used to perform limited signal conditioning on the incoming signals, and as such, it was designed using a very large–grained architecture that limited the degree of programmability.

Dudek and Hicks took yet another approach to reprogrammable hardware with their analog microprocessor [17]. Their system was modeled after a standard digital microcontroller with digital memory and digital fetch and decode control logic; however, the actual datapath was analog. They used a sampled–data approach similar to switched–capacitor systems to temporarily store values in analog registers between instructions [18]. While this research may not be directly relevant to FPAAs now, it does hold promise for the development of future FPAAs that contain advanced intellectual property (IP) modules, such as analog microprocessors similar to modern digital FPGAs.

On the software side, several different efforts are focused on various aspects of the CAD tool flow necessary for the rapid prototyping of analog and mixed-signal systems. Within the simulation and synthesis processes, it is important to have an accurate and efficient method of modeling the behavior of the generated system. Various models have been suggested including those by Enright and Mack in [25] and Long in [60]. Additionally, work has been done in the synthesis of analog circuits from user input in the form of an analog high-level description language (AHDL). Several AHDLs exist including Cadence's SpectreHDL. In one effort, Binns et al. introduced a high-level, top-down methodology for designing analog systems that are described in SpectreHDL [8]. However, with the creation of an IEEE standard AHDL that has been dubbed VHDL-AMS (VHSIC hardware description language – analog and mixed-signal), proprietary AHDLs will probably fade in popularity. Thus, the efforts of Ganesan and Vemuri in building a VHDL-AMS synthesis tool [30, 31] seem more relevant to the tool flow of future FPAAs.

Ganesan and Vemuri are developing an automated CAD tool flow for analog circuits that they call the VHDL–AMS Synthesis Environment (VASE) [30]. VASE is built on their previous work on a performance–oriented router for FPAAs [29]. The router was designed for and tested using Motorola's MPAA020 FPAAs (now sold by Anadigm [2]). As was previously noted, these devices were based on a small number of operational amplifiers and switched–capacitor technology. The design of a large–scale, functionally rich FPAA will provide researchers in the CAD tool flow arena with a more complex and more interesting platform to test and develop their automated software applications. In a similar effort, Ganesan and Vemuri have published work focusing on the partitioning of systems between the analog and digital domains [32, 33]. Again, a large–scale, mixed–signal prototyping platform will benefit this area of research by providing a viable platform to investigate the advantages and difficulties involved in the analog–digital partitioning of systems.

#### 2.5 Performance

The performance characteristics of FPAAs in regards to bandwidth, noise immunity, and signal-to-noise ratio (SNR) are important in order for FPAAs to be widely accepted by circuit designers. As with many new technologies, the initial effort on FPAAs has focused more on their functional development and proof-of-concept rather than the rigid performance parameters needed for marketable products. Thus, the single biggest unknown in designing large-scale FPAAs is the resulting performance. Often, the initial reaction to FPAAs is that the noise introduced by device mismatch and the parasitic effects of large numbers of switches will cripple the performance of any large, highly flexible FPAA.

Floating-gate devices alleviate some of these problems. Specifically, device mismatch can be compensated for by individually programming the floating-gate transistors to match in output behavior. In addition, the programmable nature of the switches will allow them to be used as variable resistors within the system, and thus, use the non-ideal nature of the switch as an active circuit element [36]. However, this does not completely solve the problem of switch parasitics, because certainly, a number of "unwanted" switches will ultimately be required in a given circuit. The effect of these floating-gate switches has been studied here and results are shown in Chapters 4 and 5. The user and/or automated compilers can use this information to optimize a given system in terms of switch routing so as to minimize their effect and meet the required performance constraints. Previous FPAAs have also been limited in bandwidth based on their underlying technology. One of the first commerical FPAAs, the EPAC device, was limited to 125 kHz at the input [49]. In general, switched–capacitor designs are typically found to have maximum frequencies in the kilohertz to low–megahertz range [35]. This is similar performance to that shown by continuous–time FPAAs with local routing [24, 69]. One of the fastest designs on record is a small FPAA with a simple CAB based on the second–generation current–conveyor. An amplifier implemented on this FPAA is shown to have a 3-dB frequency of 11 MHz, which is on the order of the performance needed for video applications [34]. While scaling up this FPAA to a meaningful size would inevitably diminish it's bandwidth, it does offer hope that future FPAAs will be able to balance flexibility, functionality, and performance.

#### 2.6 Application Focus

A general–purpose, commercially viable FPAA similar to commercial FPGAs remains elusive. Many FPAA designs have sacrificed size and generality in favor of better performance for a constrained set of circuit designs. FPAAs have been proposed for evolvable hardware [48, 72, 78], neural networks [55, 58], signal conditioning [49], programmable filters [7, 24, 69], fuzzy logic [66], machine learning algorithms [11], and high–frequency applications [34]. Other FPAA designs have attempted to focus on a broader class of systems including both linear and nonlinear elements [10, 70]. However, these efforts have failed to produce a suitably generic, user–friendly FPAA. In addition, all of the FPAAs to date have been very small. The number of CABs on a given device remains under 50 with many of the devices having less than 10 CABs. While several companies currently sell FPAA devices, the market remains relatively immature, and no single device or technology has received wide–spread acceptance.

# CHAPTER 3 BUILDING A LARGE–SCALE FPAA

As shown in Chapter 2, traditional FPAAs resemble the early PLDs in that they are focused on small systems often having only a handful of computational logic blocks and limited programmability. Likewise, an analogy can be made between modern FPGAs and the large–scale FPAAs introduced in this thesis. However, while their overall architectures may be similar, reconfigurable analog systems are not completely analogous to their digital counterparts. Developing robust, programmable analog circuits presents a number of challenges not found in the digital world. In particular, the noise sensitivity (and effects of the switch network on the results of the computation) and the design space to which programmable devices are applicable are more critical factors in designing FPAAs.

#### 3.1 Noise Sensitivity and the Effects of Switches

Analog circuits tend to be more sensitive to noise than digital designs. Because of the quantization and resulting representation of ones and zeros as discrete voltages, digital designs can tolerate a relatively large amount of noise in the system without changing the precision of the result. Problems arise only when noise levels are high enough to move a signal from a logical one to a logical zero or vice versa. In the analog domain, however, values are represented as continuous voltages or currents. Any noise in the system will directly affect the precision of the result. For reconfigurable analog systems that must rely on networks of switches to set the internal signal paths, this means that the parasitics of the switches in a signal's path can affect the result and are a critical factor in the performance of the FPAA.

Adding switches in the signal path can have several effects including the addition

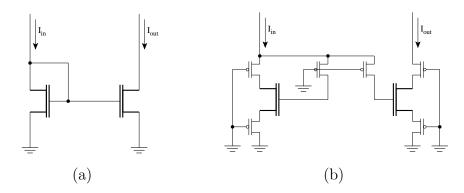

**Figure 7.** (a) A simple, two-transistor current mirror illustrates the challenges of design reconfigurable ICs with fine-grain building blocks. (b) The parasitic capacitance that results from using switches to form the current mirror will reduce the bandwidth of the system.

of parasitic capacitance, resistance, and transistor leakage currents to the path. Increased capacitance and resistance on a signal line will lower the bandwidth of the system. For example, a simple two-transistor current mirror is shown in Fig. 7a. The same circuit is shown in Fig. 7b with switches being added to the signal paths as they would need to be if the current mirror were synthesized on the FPAA using the MOSFET transistors in the CAB. In this case, there should not be any current flow between the gate nodes, so the voltage should remain equal on the two gate nodes even with the switches in the signal path. However, the parasitic capacitance will decrease the bandwidth of the current mirror.

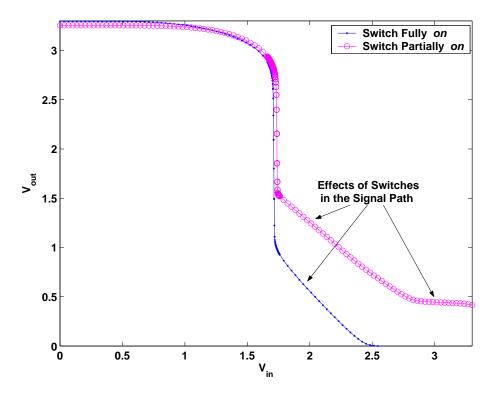

As shown in Fig. 8, other circuits that have switches in a signal path with current flowing through them will have a voltage drop across the transistor. In the case of a digital inverter (also considered a high–gain amplifier), adding switches to the sources and drains of the nFET and pFET transistors will result in an output with maximum and minimum voltages that are slightly inside the power rails (see Fig. 9). Since the switches in the FPAAs designed as a part of this thesis are pFET devices, one can expect this effect to be much worse for low voltages (i.e., ground) than voltages near the 3.3 V power rail. In this case, the parasitics also increase the rise and fall times, and thus, descrease the maximum frequency for the system.

**Figure 8.** (a) A MOSFET inverter (or high–gain amplifier) circuit diagram is shown here without the switches as it would be designed in a custom CMOS chip. (b) Synthesizing the inverter on an FPAA using switches to connect transistors from the computational logic blocks results in this circuit diagram. The switches will add parasitic capacitance as well as create a voltage drop across the transistor for those switches that have current flowing through them.

Figure 9. Here, the input to output voltage relationship is shown for an inverter that is synthesized in a testbed FPAA. The inverter is synthesized using an nFET and pFET in one of the CABs on the chip. The switches used to make the appropriate connections are shown in Fig. 8b. The effects of the switches in the signal path are evident by the uncharacteristic linear decay as the output approaches ground. Also, it is clear that when the input is High, the output is not equal to 0 V as one would expect. The switches in the signal path connecting ground to the inverter cause the output to settle to a voltage greater than 0 V due to the non-zero resistance of the switches.

#### **3.2** Switch Networks and Interconnect Design

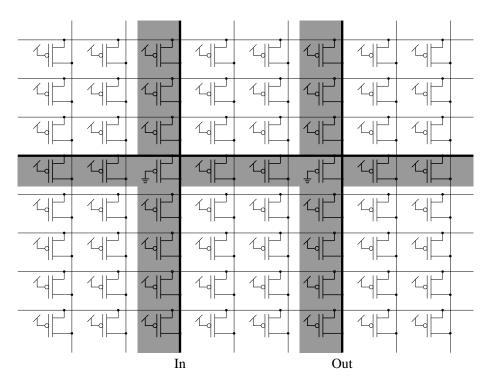

The resistive/voltage drop effects of the switches will certainly increase as more switches are added to the signal path. However, there is another subtlety involved. The parasitic capacitance and resistance added by the switches at any given switch terminal is actually the sum of all the parasitics of all the switches in a row or column. The summation of parasitics is due to the fact that all the sources for a given row of switches are tied together and that all the drains for a given column of switches are tied together. Therefore, the parasitic contribution of the switches will be present regardless of the state (on or off) of each switch. Since the primary effect of parasitics is lowering the bandwidth, an important architectural issue is present, especially if

Figure 10. A full crossbar switch provides the most interconnectivity between the components and the input/output (I/O) pins. This architecture also leads to the fewest number of switches in series in a given signal path. However, it results in the worst parasitic effects because of the large number of switches tied to each row and column.

the goal is high–speed design. As FPAAs scale up in size, designers will not be able to use large crossbar switches to make global connections without seriously limiting the bandwidth of large–scale FPAAs.

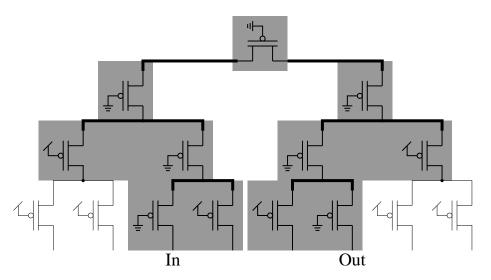

Instead, hierarchical interconnects will be necessary. By limiting the number of switch connections at each tier of routing, the maximum bandwidth can be set. However, as more tiers are added to the heirarchy, the number of switches that a signal must travel through will increase, thus increasing the resistive drop in voltage due to the routing network. Extreme examples of these two routing paradigms (crossbar vs. hierarchical) are shown in Fig. 10 and Fig. 11. In Fig. 10, a full crossbar switch is shown to illustrate the large parasitic contributions of the switches that result from this type of routing design. The transistors that contribute parasitics to the path from In to Out are highlighted. Figure 11 shows the other extreme, a binary tree. In

Figure 11. A full binary tree provides the least parasitic effects; however, it requires the most switches to be present in series in a given signal path, and has limited interconnectivity between the components and I/O pins.

this case, the parasitics at each tier of the hierarchy are minimized, but the number of switches through which a signal must pass increases rapidly with the size of the FPAA. Connectivity is also more limited in a binary tree style architecture. Large–scale FPAA designs must balance the need for bandwidth, signal degradation (number of switches in the signal path), and interconnectivity. The optimal point for this trade– off will be a function of the signal mode of the computational logic (current–mode, voltage–mode, mixed–mode), the size of the overall FPAA, the process technology used (and thus the level of parasitics present), and the bandwidth requirements of the end–user.

A compromise between the extreme routing designs is necessary. One such solution uses crossbar switch networks in the local CAB routing to provide the most connectivity and flexibility in connecting the components together. Global routing will then occur through a moderate number of tiers. For example, CABs can be clustered into megaCABs (groups of four to eight CABs), where limited routing connects CABs within each megaCAB together. These megaCABs can then be tiled across the FPAA in a mesh-style architecture with horizontal and vertical routing between the megaCAB blocks. By tiering the global routing interconnects, the routing area growth is slowed from  $O(N^2)$  to O(logN).

#### 3.3 Design Space and Computational Analog Block Design

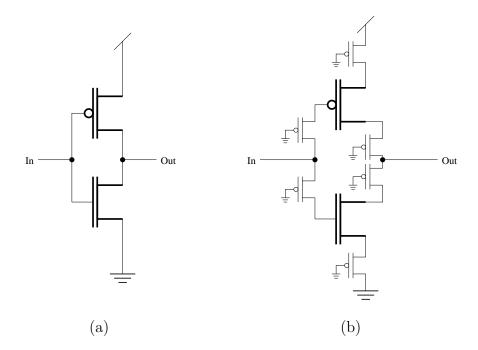

Another difference between reconfigurable analog and digital devices is the design space that each must encompass. Functionality in the digital domain can be reduced to a basic set of combinational and sequential primitives. For example, a NAND gate can be configured to implement any of the other Boolean logic gates. Thus, with a sufficiently large number of NAND gates, any combinational logic function can be achieved. Similiarly, an asynchronous read-only memory (ROM) primitive can be used to implement any combinational function. For the sequential functions, any basic storage element (e.g., flip-flop or latch) can be used to provide the necesary memory. Most modern FPGAs use asynchronous ROMs to synthesize the combinational logic and D-type flip-flops for implementing the memory/sequential logic. Thus, by replicating these two basic primitives thousands of times across a chip (and a sufficient routing network), an FPGA can be created that synthesizes a very large number of different digital systems. It is tempting to think that one might be able to do the same thing in the analog domain. However, there has not been a sufficiently generic set of medium-grained building blocks (on the same order of complexity as flip-flops or asynchronous ROMs) proposed for synthesizing a wide-range of analog circuits. To get the desired generality, one must use fine-grain building blocks, such as transistors, resistors, diodes, and capacitors. Indeed, a large number of analog systems can be built with these basic blocks; even digital systems could be synthesized with such a device. However, these primitives are so fine–grained that it would require such a large number of components—and thus a large number of switches—to implement a design that the switch parasitics would degrade the performance. For example, the circuit diagram for a basic 9-transistor operational transconductance

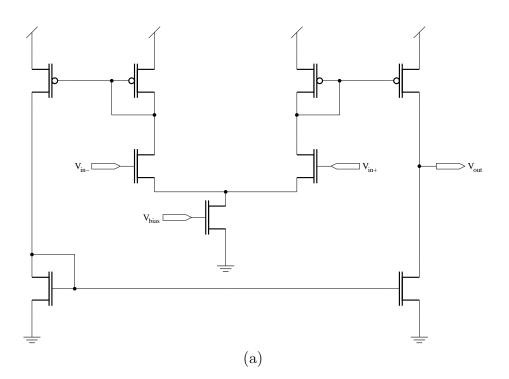

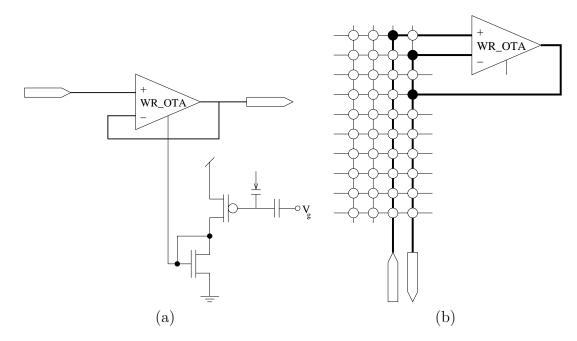

**Figure 12.** (a) The circuit diagram of a basic 9–transistor operational transconductance amplifier (OTA). (b) The circuit diagram of the same OTA with the switches needed if it is implemented on a fine–grain FPAA with only transistors. The addition of the 27 switches will dramatically reduce the performance and functionality of this circuit.

amplifier (OTA) is shown in Fig. 12a. In part (b) of this figure, the same OTA is shown with the switches necessary to synthesize this circuit on a fine–grained FPAA with transistors only. The FPAA design requires at least 27 switches, in addition to the nine transistors, to implement the OTA. The switches will drastically affect the performance and functionality of the OTA and may cause the circuit to break. To mitigate these effects, coarser–grained blocks must be used. The task then is to do so while still maintaining sufficient flexibility, functionality, and generality.

Using coarse–grain blocks can be appealing given their increase in performance and robustness over fine–grain blocks. However, if the basic building blocks in an FPAA are of too high a level, then the flexibility is greatly diminished. To be as flexible as possible, an FPAA needs to have a wide range of fine–grained, medium– grained, and coarse–grained components. This means that there will often be more than one way of synthesizing the same system on the FPAA. This provides the most flexibility to end–users, because they can vary the levels of performance, utilization, flexibility, and complexity. For example, a CAB could contain a high–level cell for bandpass filtering, several OTAs, and several pFET and nFET transistors. If there are a sufficient number of CABs, then a bandpass filter could be implemented in at least three ways:

- 1. Specialized bandpass filter block: The specialized cell in one of the CABs could be used directly. This is the simplest implementation method, and it will provide the highest performing design. However, since the full circuit is set in silicon, this will provide the least flexibility in terms of specifying the filter parameters and circuit topology.

- 2. *OTA-level Design:* The OTAs located in CABs could be connected via the switch network to implement a number of different circuit topologies. This design method will result in lower performance than the first method, but it gives the end-user a lot more flexibility and input into the filter specifications.

Here, the only fixed parameter is the type of OTA that is used in the CABs.

3. Transistor-level Design: The transistors located in the CABs could be used to synthesize different operational amplifiers or other medium-sized blocks, which could then be wired together as in method two to form a bandpass filter module. Obviously, this would result in a large number of switches in the signal paths, and thus, it would use alot of the routing infrastructure and would be plagued with large parasitics. Because of the large number of switches used in this design, it would result in the lowest performance (assuming basic functionality can be achieved at all), but it would result in the highest degree of freedom in specifying the circuit topology and filter parameters.

The perfect CAB is elusive indeed. However, careful analysis of common circuit topologies can lead one to a group of components that strike a reasonable balance between flexibility, performance, and generality. Also, one should not limit designs to homogeneous meshes of CABs. In reality, the overall architecture presented in this thesis is designed to be a framework that can be used with many different CABs, while not requiring changes to the overall infrastructure. It is forseen that a number of different CABs will be tried and used in various circuit genres. For example, one can imagine FPAAs targeted at problems in audio processing, image processing, neuromorphic signal processing, telecommunications, etc. These different FPAAs need not largely differ. Instead, a reasonably general–purpose CAB can be tiled across the FPAA with special–purpose CABs targeted at each genre interspersed among them. This type of architecture is very similar to modern FPGAs, where a mesh of general– purpose logic blocks (i.e., asynchronous ROMs and D flip–flops) is interspersed with specialized blocks, such as dense memory blocks, hardware multipliers, digital filters, and even entire processor cores.

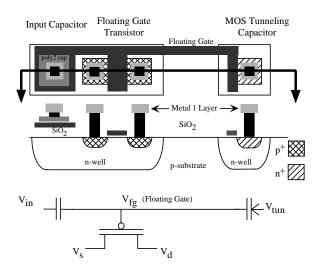

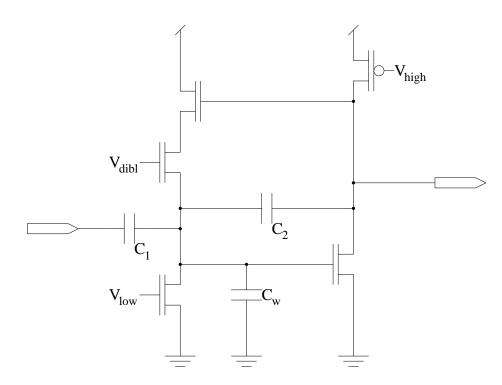

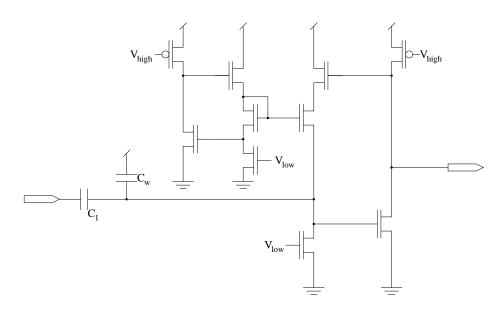

Figure 13. Layout, cross section, and circuit diagram of the floating–gate pFET in a standard double–poly, n-well MOSIS process: The cross section corresponds to the horizontal line slicing through the layout view. The pFET transistor is the standard pFET transistor in the n-well process. The gate input capacitively couples to the floating–gate by either a poly–poly capacitor, a diffused linear capacitor, or a MOS capacitor, as seen in the circuit diagram (not explicitly shown in the other two figures). Between  $V_{tun}$  and the floating–gate is our symbol for a tunneling junction—a capacitor with an added arrow designating the charge flow.

# 3.4 Floating–gate Technology in Programmable Analog Circuits

Previous FPAAs have suffered from their small size and lack of functionality/generality. Next–generation FPAAs need to correct these problems in order to extend the usefulness and acceptance of FPAAs. Ideally, one would like a small, easily programmable element that can be configured to act as an ideal switch, variable resistor, and configurable computational element. While such a device is indeed ideal, floating–gate transistors do offer some of these qualities. Previously, we have shown that the floating–gate transistor can be used as a (nonideal) switch, variable resistor, and programmable element within larger computational blocks (e.g., analog multiplier, programmable filter, programmable OTAs, etc.) [36].

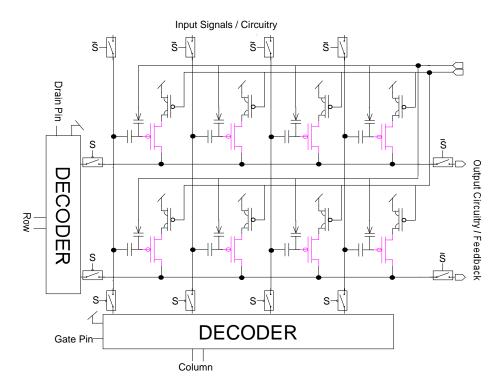

In addition, the small size of the floating-gate structure will allow larger, more

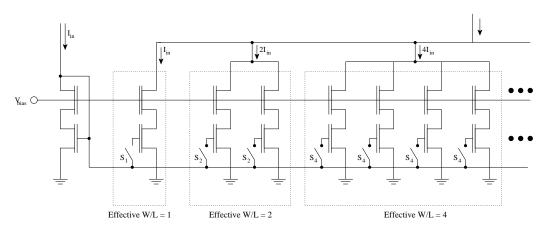

**Figure 14.** Standard designs often achieve circuit programmability by embedding switchable arrays of elements (such as transistors or capacitors) within the logic cells. Here, a conceptual version of [65]'s programmable current mirror is shown. In their case, 5 bits were used to set the switches. This required 64 MOS transistors, 31 digitally controlled switches, and five memory cells to hold the configuration of the switches. Using floating–gate technology, this entire structure can be replaced with two programmable floating–gate transistors.