Our Approach

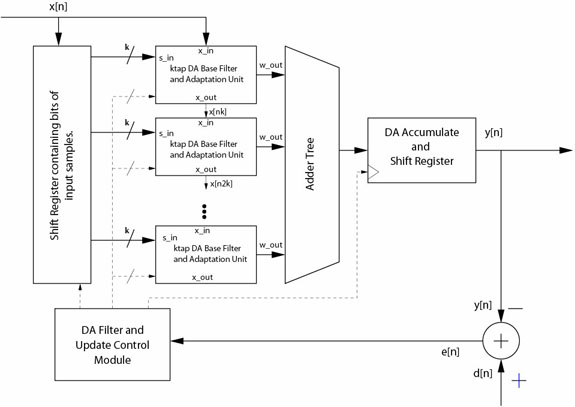

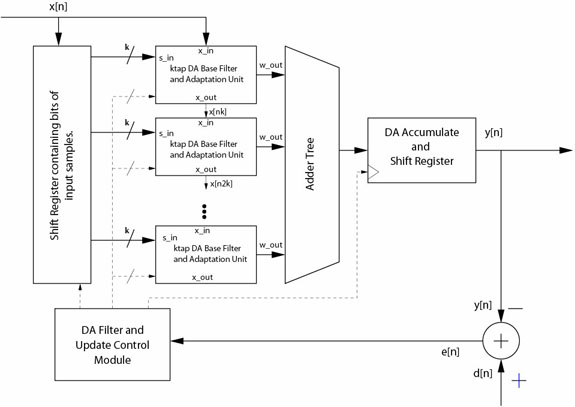

We construct the DA-based adaptive LMS filter as shown:

Each

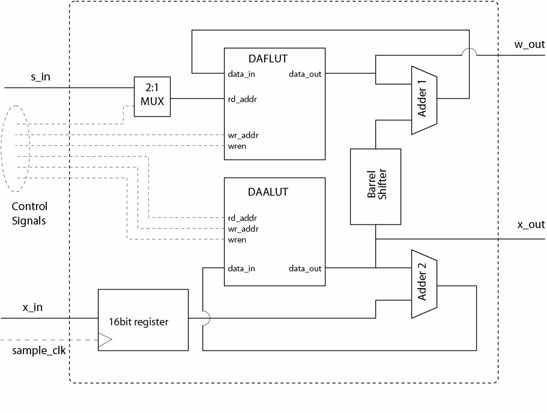

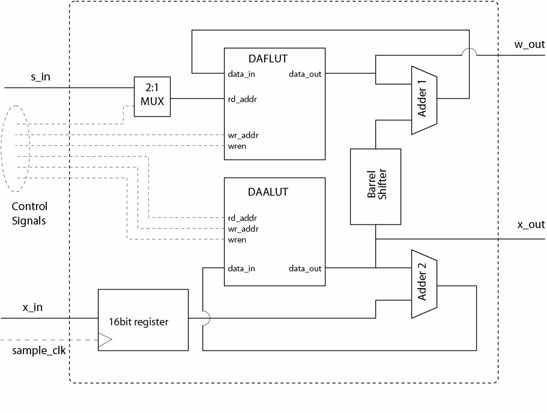

Base Filter and Adaptation Unit is composed of the following:

The memory

DAFLUT contains the weights and all possible sums of the weights, and the memory

DAALUT contains all possible combinations of sums of the most recent samples.